Quick Specs

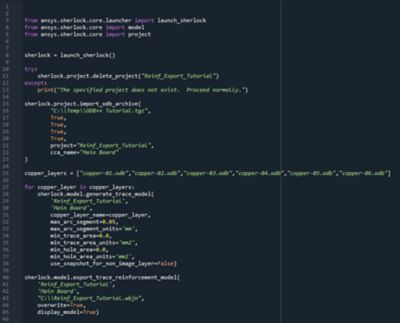

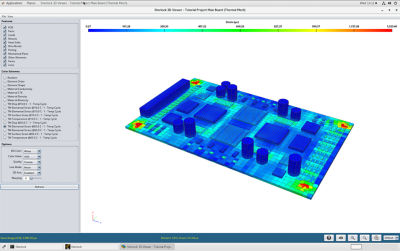

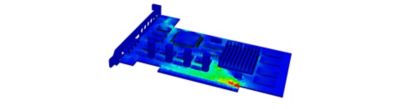

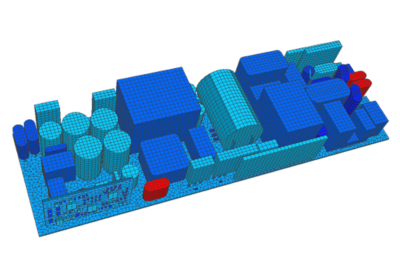

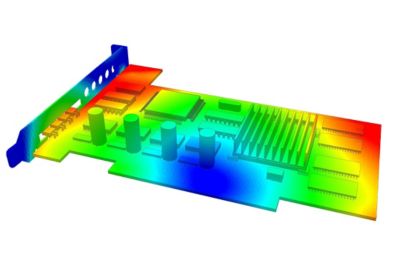

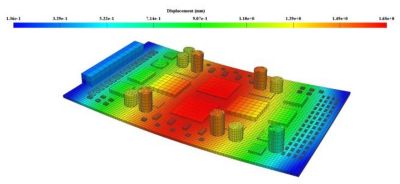

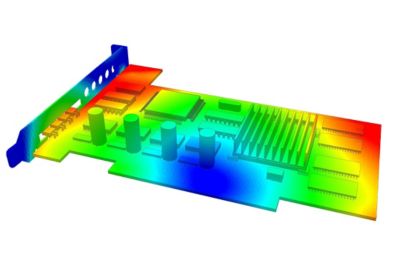

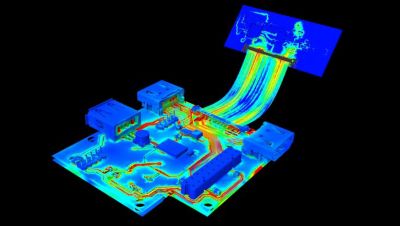

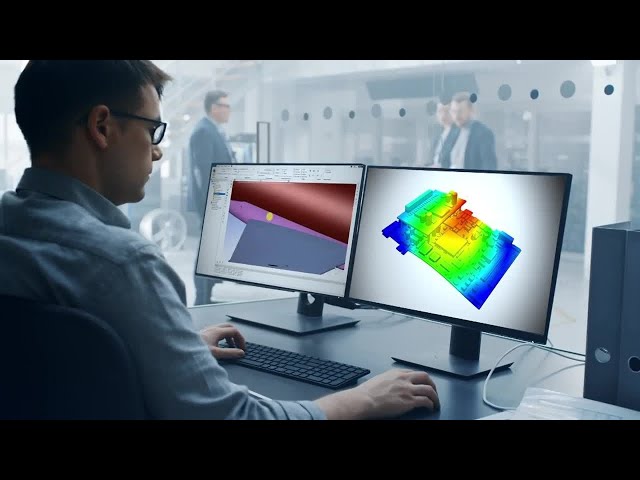

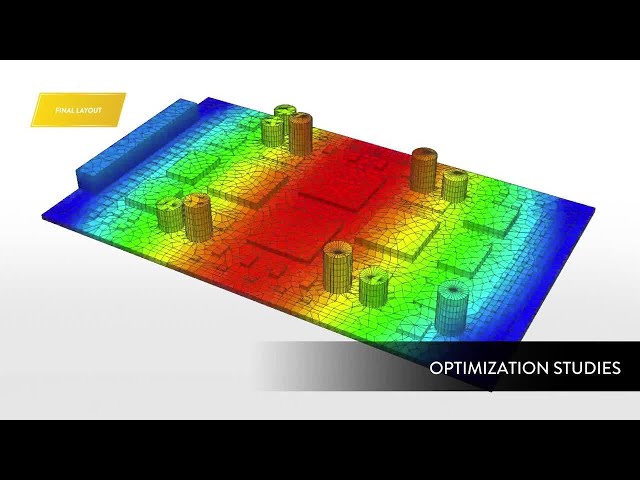

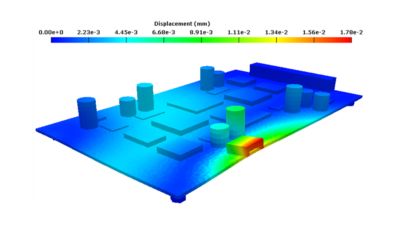

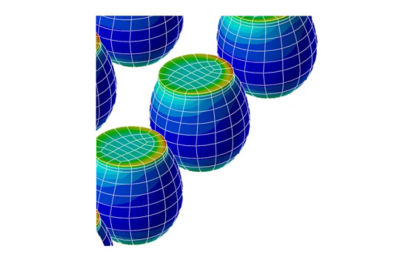

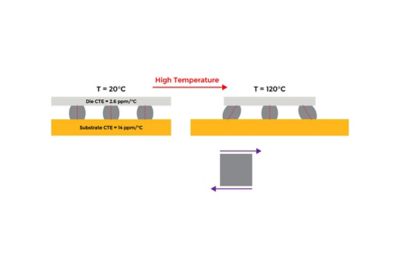

With embedded libraries containing over one million parts, Sherlock rapidly converts electronic computer-aided design (ECAD) files into computational fluid dynamics (CFD) and finite element analysis (FEA) models. Each model contains accurate geometries and material properties and translates stress information into validated time-to-failure predictions. Sherlock parts databases also include a link to Ansys Granta Materials Selector.